# ПОДХОДЫ К ПРОЕКТИРОВАНИЮ ВЫЧИСЛИТЕЛЕЙ В СИСТЕМАХ ТЕХНИЧЕСКОГО ЗРЕНИЯ

© 2010 г. И. А. Аслеев

НПК “Государственный оптический институт им. С.И. Вавилова”, Санкт-Петербург

E-mail: point\_igor@list.ru

Рассматриваются различные подходы к построению вычислителей для систем технического зрения, анализируются их достоинства и недостатки. Приведен пример реализации рекурсивного фильтра с использованием микросхемы программируемой логики.

**Ключевые слова:** обработка изображений, техническое зрение, цифровые сигнальные процессоры, программируемые логические интегральные схемы.

Коды OCIS: 150.1135, 150.4065

Поступила в редакцию 16.06.2010

## Введение

Развитие современной элементной базы существенно расширяет возможности разработчиков систем видеоанализа. Если буквально 20 лет назад задачи автоматического распознавания требовали использования суперкомпьютеров, то сейчас появилась возможность решения этих задач с помощью процессоров, используемых в массовых бытовых приборах. Однако даже применение современной элементной базы не снимает всех проблем разработчиков. Основные из них – довольно высокие требования к производительности и пропускной способности вычислительных систем. Поясним на примере. Согласно стандарту PAL [1], телевизионный кадр имеет разрешение  $768 \times 576$  и передается с частотой 25 кадров в секунду, используя для кодирования яркости пикселя 8 разрядов (1 байт), получаем около 11 млн байт/с. Именно такую пропускную способность должна обеспечивать система технического зрения, работающая в масштабе реального времени.

Рассмотрим классическую цифровую схему:

Вх. сигнал → ФНЧ → АЦП → ВЫЧИСЛИТЕЛЬ →

→ ЦАП → Вых. сигнал.

Здесь ФНЧ – фильтр нижних частот, АЦП – аналого-цифровой преобразователь, ЦАП – цифро-аналоговый преобразователь.

Если вопросы оцифровки и обработки, операции получения из цифровых данных соответствующего уровня аналогового сигнала можно

считать устоявшимися, то подходы к созданию вычислителя непрерывно совершенствуются. Рассмотрим некоторые из них.

## Последовательный метод

Наиболее простым является так называемый последовательный метод. Как правило, при таком подходе непосредственно в качестве вычислителя используется цифровой сигнальный процессор (ЦСП). Современные ЦСП работают на частотах выше 1 ГГц, однако развитие ЦСП идет не только в направлении повышения частоты, огромное влияние на производительность оказывает также архитектура процессора. Наличие в чипе различных периферийных устройств (устройств прямого доступа к памяти (ПДП), контроллеров внешней памяти, различных приемопередатчиков) позволяет эффективно использовать вычислительные возможности ЦСП.

Рассмотрим на примере ЦСП фирмы TI (*Texas Instruments*) марки TMS320c6416 [2]. Это современный ЦСП, выполненный по 90-нанометровой технологии. ЦСП состоит из 2-х независимых вычислительных блоков, каждый из которых в свою очередь состоит из 4-х устройств. Применение технологии *VelociTI* (усовершенствованное VLIW – *Very-Long-Instruction-Word*) дает возможность загружать все вычислительные блоки одновременно. Таким образом, при функционировании на частоте 1 ГГц пиковая производительность данного ЦСП определяется по формуле  $8(\text{unit}) \times 1 \text{ Гц}$  [2]. Не стоит за-

бывать, что это пиковая производительность, достижимая при 100% загрузке ядра ЦСП, в реальных задачах обработки изображений она существенно ниже и будет зависеть от конкретной реализации алгоритмов.

Также разработчики не обошли вниманием вопросы организации памяти, что является существенным при разработке систем видеообработки в масштабе реального времени. Процессор TMS320c6416 имеет 1 Мбайт внутренней статической памяти с временем доступа в 1 процессорный такт, а также позволяет подключать во внешнийшине EMIF (*external memory interface*) различные типы памяти SDRAM (*Synchronous Dynamic Random Access Memory*, *Flash-Memory* и др.) [2].

Процессор имеет 1 Мбайт внутренней памяти, что недостаточно для хранения всего видеокадра, а использование для этого внешней памяти существенно увеличивает “накладные расходы” для чтения/записи необходимых данных, что может привести к нереализуемости сложных алгоритмов.

Наличие аппаратных контроллеров кэш-памяти позволяет отчасти решить проблему использования внешней SDRAM, однако для некоторых задач этого может оказаться недостаточно. Таким образом, разработчикам, проектирующим системы, функционирующие в масштабе реального времени, приходится искать другие подходы для решения поставленных задач. Для этого, как правило, используется разбиение всего кадра на подкадры, либо переходят от работы по всему кадру к работе по строкам изображения, однако это не всегда до-

пустимо и существенно увеличивает время разработки.

В качестве достоинств последовательного метода можно привести сравнительную гибкость и простоту разработки приложений ЦСП. Недостатком данного подхода является невысокая производительность конечных устройств.

Принимая во внимание то, что стандартные алгоритмы цифровой обработки сигналов (ЦОС), воплощающие конечную импульсную характеристику, бесконечную импульсную характеристику и быстрое преобразование Фурье, представляют собой простейшие операции над пикселями, поступающими с высокой частотой, можно перейти ко второму способу реализации систем реального времени – использованию программируемой логической интегральной схемы (ПЛИС, англ. *programmable logic device*, PLD).

### **Параллельный метод**

ПЛИС – электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задается посредством программирования. Примером ПЛИС является микросхема *Cyclone III EP3C5* производства фирмы ALTERA (табл. 1).

Для иллюстрации практического применения методов аппаратной реализации алгоритмов ЦОС на ПЛИС рассмотрим детально процесс разработки блока, выполняющего межкадровую рекурсивную однополюсную фильтрацию [3].

**Таблица 1. Параметры микросхемы *Cyclone III EP3C5***

| Ресурсы ПЛИС                      |                                                                                                                                                                                                              | EP3C5                           |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Логический объем и быстродействие | Количество логических элементов<br>Объем встроенного ОЗУ, Кбит<br>Кол-во блоков встроенного ОЗУ М9К<br>(8 Кбит+1024 бита честности)                                                                          | 5,136<br>414<br>46              |

| Особенности                       | Количество встроенных умножителей 18×18-бит/9×9-бит<br>Блоки двухпортового ОЗУ<br>Количество глобальных и локальных цепей тактирования<br>Количество PLL/выходов PLL<br>Размер конфигурационного файла, Мбит | 23/46<br>+<br>10<br>2/10<br>2,8 |

| Доступность                       | Доступность в индустриальном температурном исполнении<br>Доступность в бессвинцовом ( <i>Lead-Free</i> ) исполнении                                                                                          | +                               |

## Алгоритм

Пусть  $X(t)$  и  $Y(t)$  – исходное и результирующее изображения,  $t$  – номер кадра. Рекурсивный однополосный фильтр описывается выражением следующего вида:

$$Y(t) = (1 - k)X(t) + kY(t - 1), \quad (1)$$

коэффициент  $k$  может быть найден следующим образом:

$$k = \exp(-1/d), \quad (2)$$

здесь  $d$  – постоянная времени фильтра. Переходная характеристика данного фильтра такова, что за количество отсчетов (кадров), равное  $3d$ , переходный процесс считается завершенным. Исходя из этого, можно сформулировать требование к изображениям: во избежание искажений объектов изображение не должно меняться в течение времени  $3d$ . Таким образом, малоподвижным изображением для рассматриваемого метода является такое изображение, которое не меняется за время  $3d$ , где  $d$  измеряется в кадрах.

В том случае, если выражение (1) привести к виду

$$Y(t) = X(t) + k[Y(t - 1) - X(t)], \quad (3)$$

для воплощения фильтра потребуется всего лишь один умножитель.

## Выбор формата представления чисел

Пусть отсчеты входного изображения – целые положительные 10-ти разрядные числа. Отсчеты выходного изображения – положительные 16-ти разрядные числа с фиксированной точкой в формате 10Q16, где старшие 10 разрядов – целая часть. Порядок действий в выражении (3) имеет следующий вид:

1.  $R1 = Y(t - 1) - X(t)$ ,

2.  $R2 = kR1$ ,

3.  $Y(t) = X(t) + R2$ .

В первом действии операнд  $Y(t - 1)$  – положительное число в формате 10Q16 без знака. Операнд  $X(t)$  необходимо преобразовать в тот же формат путем добавления нулевой дробной части. Результат будет в формате 11Q17 со знаком.

В действии 2 необходимо выбрать разрядность  $k$ . Результат должен быть в формате 11Q17 со знаком, младшая часть результата умножения отбрасывается. Следовательно, максимальная разрядность для  $k$  может быть 0Q16. Однако практически такая точность не требуется, например, при формате 0Q4 максимальное значе-

ние  $k$  составит  $15/16 = 0,9375$ , продолжительность переходного процесса (“время накопления”)  $t$  составляет  $-3/\ln(k) \approx 46$  кадров, т. е. 2 с.

Данного времени переходного процесса на практике достаточно, следовательно, и для  $k$  достаточно разрядности 0Q4.

В третьем действии результат предполагается положительным, знаковый разряд отбрасывается.

## Интерфейс и блок-схема

Интерфейс блока, выполняющего межкадровую фильтрацию, на языке Verilog представлен в табл. 2.

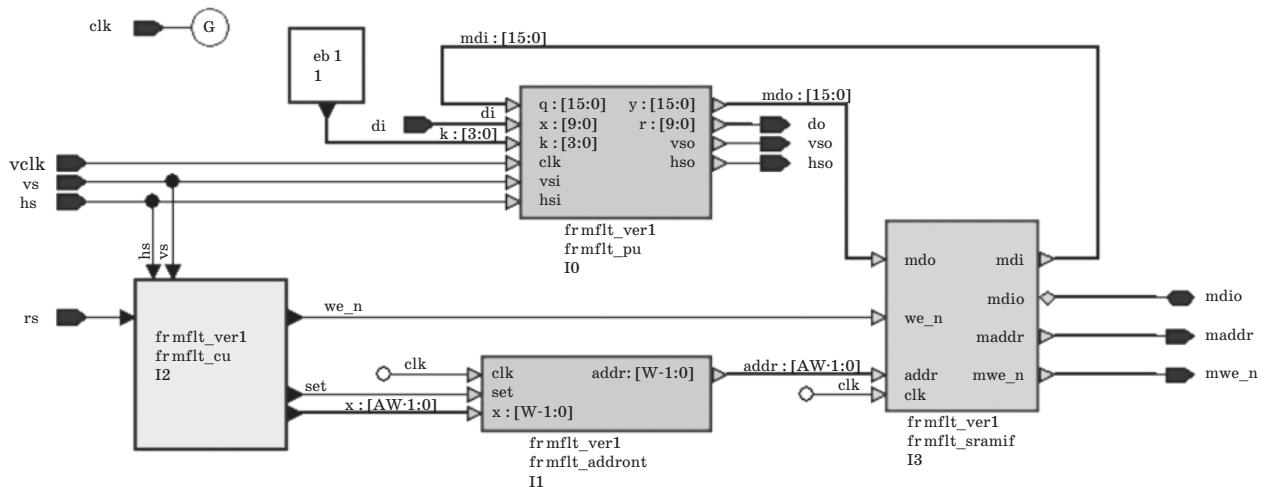

Блок-схема фильтра, представленная на рис. 1, содержит следующие блоки: frmflt\_ru – операционное устройство, frmflt\_cu – управляющий автомат, frmflt\_addrct – счетчик адреса памяти, frmflt\_sramif – интерфейс с внешней памятью SRAM (*Static Random Access Memory*).

Организация ввода коэффициента  $k$  на данном этапе не рассматривается и  $k$  предполагается постоянным.

## Операционное устройство

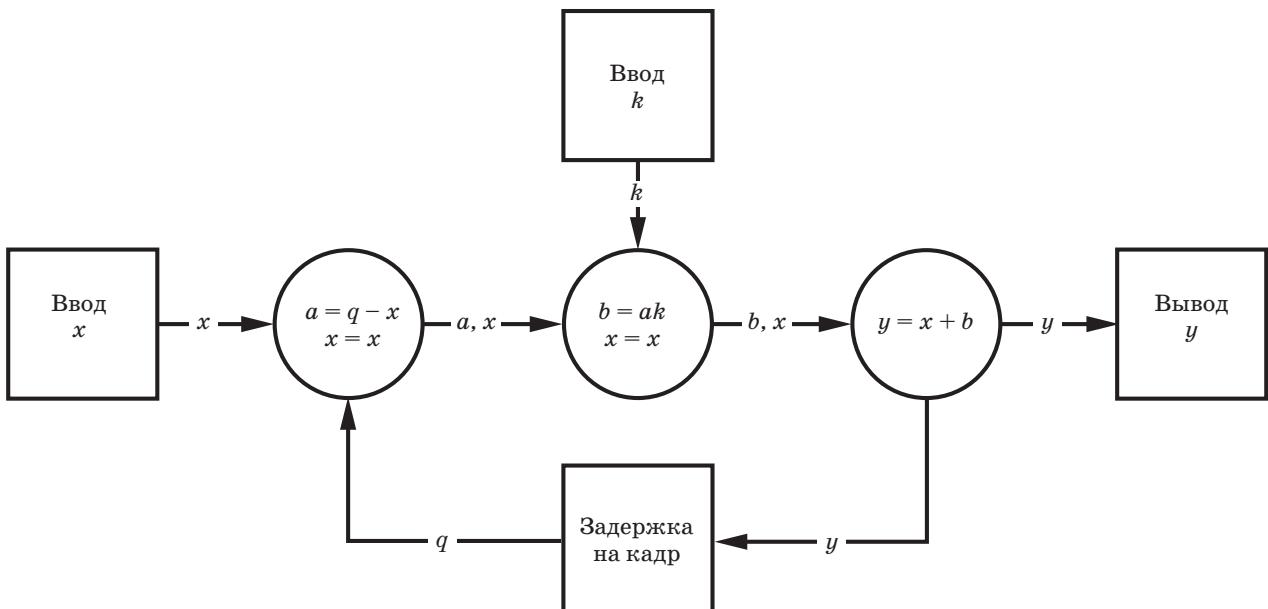

Операционное устройство выполняет все математические действия, описываемые выражением (3). Диаграмма потока данных для операционного устройства представлена на рис. 2.

Предполагается, что каждый процесс, или параллельно исполняемая подпрограмма (блоки круглой формы), выполняет определенные действия и сохраняет выходные данные в ре-

Таблица 2. Интерфейс блока межкадровой фильтрации

```

module frmflt(

// global

clk,           // clock

rs,            // reset

// data input

vs,             // vertical sync

hs,             // horizontal sync

vclk,          // video clk

di,             // data in

// data output

vso,            // vertical sync

hso,            // horizontal sync

do,             // data out

// memory interface

maddr,          // memory address

mwe_n,          // memory write enable (active low)

mdio,           // memory data io

);

```

страх, таким образом, организуется конвейерная обработка. Значения  $x$  передаются от процесса к процессу для выравнивания задержек. Запаздывание конвейерной схемы равняется трем, это запаздывание должно быть компенсировано при организации задержки на кадр.

### Управляющий автомат

Управляющий автомат предназначен для организации процесса задержки на кадр и компенсации запаздывания. Задержка на кадр выполнена на основе оперативного запоминающего устройства (ОЗУ) типа SRAM и счетчика адреса.

Одним из главных преимуществ ПЛИС является возможность распараллеливания вычислений, что позволяет выполнять различные действия над данными одновременно, что невозможно осуществить на классическом ЦСП. Однако перенесение на ПЛИС сложных алгоритмов, таких как автоматическое распознавание, требует существенно больших трудозатрат, чем при использовании ЦСП [3].

Выход из проблемы в использовании обоих подходов к решению задачи. Таким образом, мы подошли к следующему методу – разработке специализированных вычислителей.

Рис. 1. Блок-схема межкадрового рекурсивного фильтра.

Рис. 2. Операционное устройство.

## **Комбинированный метод**

При проектировании специализированных вычислителей задачи цифровой обработки, обычно, распределяются следующим образом.

На микросхеме ПЛИС реализуются функции приема входного сигнала, его предварительной обработки, буферной памяти с двойным доступом (для ПЛИС и ЦСП), выдачи обработанного сигнала на монитор или для его дальнейшей обработки в ЦСП.

Предварительная обработка, как правило, включает в себя различные типы фильтрации (медианная, по Собелю и проч.), увеличение динамического диапазона, коррекцию неравномерности фотоприемника, контрастирование и другие операции над пикселями.

На ЦСП реализуются алгоритмы, работающие по всему кадру – сегментация и анализ изображений, распознавание образов.

Наличие буферной памяти позволяет более эффективно задействовать внутреннюю память ЦСП, а также экономить процессорное время на операциях копирования больших массивов данных. ПЛИС может быть соединена с ЦСП как с помощью контроллера EMIF, так и через контроллер HPI (*Host Port Interface*), имеющийся в процессоре TMS320c6416.

Грамотная организация работы с памятью при максимальном использовании контроллера ПДП позволяет наиболее эффективно реализо-

вать ресурсы ЦСП, что приводит к существенному увеличению производительности всей системы в целом.

## **Заключение**

В заключение следует добавить, что описанные в данной статье методы не охватывают всего многообразия различных подходов к решению задач проектирования вычислителей для видеоанализа. Из наиболее распространенных необходимо отметить вычислители, построенные с использованием специализированных микросхем (*ASIC – application-specific integrated circuit*) либо матричных процессоров.

## **ЛИТЕРАТУРА**

1. Бондаренко А.В., Докучаев И.В., Стешенко В.Б. Аппаратная реализация систем ввода, обработки, хранения и вывода изображений различных телевизионных форматов и стандартов // Цифровая обработка сигналов. 2003. № 1. С. 27.

2. Грибачев А.А. TMS320C641x: новые рекорды Texas Instruments в области сверхмощных цифровых сигнальных процессоров // Цифровая обработка сигналов. 2001. № 1. С. 50–53.

3. Анисимов И.Ю., Малышев И.А. Методика синтеза специализированных параллельных вычислительных структур цифровой обработки изображений // Оptический журнал. 2006. Т. 73. № 3. С. 35–44.